# LSI-11 Systems Service Manual

Volume II

Prepared by Educational Services of Digital Equipment Corporation Preliminary, April 1978 1st Edition, March 1979 1st Edition (Rev), September 1979 2nd Edition, November 1980 3rd Edition, August 1982 4th Edition, November 1982 5th Edition, January 1985

© 1978, 1979, 1980, 1981, 1982, 1985 Digital Equipment Corporation.

All Rights Reserved.

Printed in U.S.A.

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The manuscript for this book was created on a Digital Word Processing System and, via a translation program, was automatically typeset on Digital's DECset Integrated Publishing System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digital   | Micro PDP-11 | RSX            |

|-----------|--------------|----------------|

| DEC       | MicroVAX     | RT             |

| DECmate   | PDP          | UNIBUS         |

| DECUS     | P/OS         | VAX            |

| DECwriter | Professional | VMS            |

| DIBOL     | Q-Bus        | VT             |

| LSI-11    | Rainbow      | Work Processor |

| MASSBUS   | RSTS         |                |

# CONTENTS

#### **VOLUME I - SYSTEMS CONFIGURATIONS**

| GENEF  | RAL CONFIGURATION RULESGENERAL CONFIGURATION RULES                                                                                                                                             | 1<br>6         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| MICRO  | J/PDP-11 SYSTEM                                                                                                                                                                                |                |

| PDP-11 | IV03 AND PDP-11T03 SYSTEMS                                                                                                                                                                     | 35             |

| PDP-11 | T03-L AND PDP-11V03-L SYSTEMS                                                                                                                                                                  | 19             |

| PDP-11 | IV23 AND PDP-11T23 SYSTEMS       6         PDP-11V23 SYSTEM       6         PDP-11T23 SYSTEM       7                                                                                           | 33             |

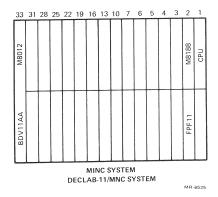

| PDP-11 | I/03-BASED MINC/DECLAB-11/MINC SYSTEMS                                                                                                                                                         | 31             |

| PDP-11 | 1/23-BASED MINC/DECLAB-11/MINC SYSTEMS       10         MINC       10         DECLAB-11/MNC PDP-11/23-BASED SYSTEM       11                                                                    | )1             |

| PDP-11 | 1/23 PLUS SYSTEM       12         GENERAL       12         COMPONENTS       12                                                                                                                 | 23             |

| PDP-11 | I/23S SYSTEM       13         KDF11-B PROCESSOR MODULE (CPU) (M8189)       13         KDF11-B LED INDICATORS       13         MSV11-D MOS RAM MEMORY       14         EXPANSION RULES       14 | 37<br>39<br>11 |

| PDP-11/23 PLUS, MICRO/PDP-11 AND MicroVAX EXPANSION | 151<br>151 |

|-----------------------------------------------------|------------|

|                                                     |            |

| VT103 LSI-11 VIDEO TERMINAL                         | 15/        |

| GENERAL                                             |            |

| LSI-11 BACKPLANE                                    |            |

| CONFIGURATION                                       |            |

| STANDARD TERMINAL PORT                              |            |

| VT1X3-MM MAINTENANCE MODULE (M8208)                 | 162        |

| 11MDS-A MICROCOMPUTER DEVELOPMENT SYSTEM            |            |

| GENERAL                                             |            |

| SPECIFICATIONS                                      |            |

| CONFIGURATION                                       |            |

| SYSTEM VERIFICATION PROGRAM                         | 185        |

| COMMERCIAL SYSTEMS                                  | 189        |

| D315 DATASYSTEM                                     | 189        |

| D322                                                | 211        |

| D324                                                | 222        |

| D325                                                | 232        |

| D333C                                               | 235        |

| D335C                                               |            |

| D336C                                               | 239        |

| DPM23 DISTRIBUTED PLANT MANAGEMENT SYSTEM           | 243        |

| LABORATORY SYSTEMS                                  | 257        |

| PDP-11L03                                           |            |

|                                                     |            |

| TELEPHONE COMPANY SYSTEM                            | 269        |

| CC1A PDP-11V03 SYSTEM                               |            |

|                                                     |            |

|                                                     |            |

| OPTIONS                                             |            |

| GENERAL MODULE INFORMATION                          | 291        |

| BA11-M MOUNTING BOX                                 | 292        |

| BA11-N MOUNTING BOX                                 | 304        |

| CONFIGURATION                                       |            |

|                                                     |            |

| BA11-S MOUNTING BOX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 325 |

| POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 328 |

| FRONT PANEL SWITCHES AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| FRONT PANEL BEZEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 334   |

| H9276 BACKPLANE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 335 |

| EXPANSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 338 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| BA11-VA MOUNTING BOX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 341 |

| GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 341 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| H349 DISTRIBUTION PANEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 345 |

| GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 345 |

| OLIVE II C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| H780 POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 347 |

| 11/00 1 04/211 0011 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| H786/H7861 POWER SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 352 |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 352 |

| of Lon to the manner of the contract of the co |       |

| H7864 POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 355 |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 355 |

| of Lon to the manner of the control  |       |

| H9275 BACKPLANE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 358 |

| GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 358 |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 359 |

| CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 360 |

| INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 362 |

| INOTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| H9276 BACKPLANE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 364   |

| GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 364   |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 365   |

| CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 366   |

| CONTIGORATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| H9278-A BACKPLANE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 368   |

| GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 368   |

| GENELIAE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |