# DECrouter 200 Technical Manual

Order No. EK-DR200-TG-001

January 1987

The DECrouter 200 Technical Manual provides general operating instructions, detailed hardware logical functions, and diagnostic software information.

Supersession/Update Information:

This is a new manual

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1987 by Digital Equipment Corporation All Rights Reserved.

Printed in U.S.A.

The postage-prepaid Readers Comments form on the last page of this document requests the user's critical evaluation to assist us in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

DEC Micro/RSX TOPS-10 **MicroVAX DECconnect** TOPS-20 **DECmate MicroVMS ULTRIX-32 DECnet** PDP ULTRIX-32m **DECserver** P/OS **UNIBUS DECtape Professional** VAX **DECUS VAXmate** Rainbow **DECwriter RSTS VAXcluster** DIBOL RSX VAX/VMS e regulation ( RSX-11M-PLUS VMS RT VT **MASSBUS**

MicroPDP-11 ThinWire Work Processor

Bell is a trademark of Bell Telephone Companies.

IBM is a registered trademark of International Business Machines Corporation.

MC68000 is a trademark of Motorola, Inc.

PC/XT and Personal Computer AT are trademarks of International Business Machines Corporation. Teflon is a trademark of E.I. du Pont de Nemours & Company, Inc.

This manual was produced by Networks and Communications Publications.

### **Contents**

### Proface

| 1.1    | DECrouter 200 Introduction                         |

|--------|----------------------------------------------------|

| 1.1.1  | Firmware                                           |

| 1.1.2  | Programmable Timers 1-2                            |

| 1.2    | Ethernet Interface System                          |

| 1.2.1  | Local Area Network Controller for Ethernet (LANCE) |

| 1.2.2  | Serial Interface Adapter (SIA)                     |

| 1.2.3  | Service Node and Load Host 1-2                     |

| 1.2.4  | Firmware and Software 1-2                          |

| 1.3    | Connector Panel Element Description 1-3            |

| 1.3.1  | Controls and Connectors 1-3                        |

| 1.3.2  | Switch S1 1–4                                      |

| 1.3.3  | Asynchronous Ports (J1 – J8)                       |

| 1.3.4  | Ethernet Transceiver Port 1-4                      |

| 1.3.5  | AC Line Voltage Input Selector Switch 1-4          |

| 1.3.6  | AC Power Cord Receptacle 1-4                       |

| 1.3.7  | AC Circuit Breaker 1-4                             |

| 1.3.8  | Power-Up and Initialization. 1-5                   |

| 1.3.9  | Initialization Sequence 1–5                        |

| 1.4    | Ethernet Systems 1–5                               |

| 1.4.1  | System Elements 1–6                                |

| 1.4.2  | Configuration Criteria 1-8                         |

| 1.4.3  | Communications Methods 1~9                         |

| 1.4.4  | Network Access and Communication Protocol 1-9      |

| 1.4.5  | Network Access 1–9                                 |

| 1.4.6  | Collision Detection                                |

| 1.4.7  | Data Frame Format                                  |

| 1.4.8  | Ethernet Characteristics 1-11                      |

| Self-T | est                                                |

| 2.1    | General 2-1                                        |

| 2.2    | Self-Test Operating Modes 2-1                      |

| 2.2.1  | Normal Mode 2-1                                    |

| 2.2.2  | Manufacturing Mode                                 |

| 2.2.3  | Initialized Mode2-2                                |

| 2.2.4  | Fatal Error Mode 2–3                               |

| 2.2.5  | Error Types 2–3                                    |

| 2.2.6  | Nonfatal Errors2-3                                 |

| 2.2.7  | Nonfatal Error Status2-3                           |

| 2.2.8  | Fatal (Hard) Errors                                |

| 2.2.9  | Using the Diagnostic LED (D2)                      |

|   | 2.2.10     | Self-Test Program Tests                                      | -5          |

|---|------------|--------------------------------------------------------------|-------------|

|   | 2.2.10.1   | Processor Register Test — ST\$CPU_REG_J                      | -6          |

|   | 2.2.10.2   | Self-Test UN-JAM Test — ST\$JAM_TEST_J2-                     | -6          |

|   | 2.2.10.3   | RAM Quick Verify Test — ST\$QUICK_RAM_J 2-                   | -7          |

|   | 2.2.10.4   | Extended RAM Test — ST\$EXTENDED_RAM_J 2-                    | -7          |

|   | 2.2.10.5   | Stuck-at Interrupt Test — ST\$STUCK_INTERRUPTS_J 2-          | -7          |

|   | 2.2.10.6   | Refresh Timer Test — ST\$REFRESHTIMER                        | -7          |

|   | 2,2.10.7   | LANCE Register Test — LANSREG_TEST 2-                        |             |

|   | 2.2.10.8   | Watchdog Timer Test — ST\$WD_TIMER                           |             |

|   | 2.2.10.9   | General Purpose Timer Test — ST\$GP_TIMER2-                  | -7          |

|   | 2.2.10.10  | Test Loader — ST\$LOADER                                     | -7          |

|   | 2.2.10.10  | PROM CRC Test — ST\$PROM_CRC 2.                              | -7          |

|   | 2.2.10.11  | NI Address PROM Checksum Test — ST\$NL_ADDRESS 2-            |             |

|   |            | Parity Logic Test — ST\$PARITY                               |             |

|   | 2.2.10.13  | EEPROM Read/Write Test — ST\$EEPROM_RW                       |             |

|   | 2.2.10.14  |                                                              |             |

|   | 2.2.10.15  | Reset to Factory Test — ST\$RESET_TO_FACTORY                 | ~D          |

|   | 2.2.10.16  | EEPROM Checksum Test — ST\$EEPROM_CS                         | -B          |

|   | 2.2.10.17  | Modem Control Signais Test — ST\$MODEM_CS 2-                 | ~8<br>~     |

|   | 2.2.10.18  | Request-to-Send — Test ST\$RTS_CTS2-                         | -8          |

|   | 2.2.10.19  | LANCE Reject Physical Address Test — LANSREJECT_PHY 2-       | -8          |

|   | 2.2.10.20  | LANCE Accept Physical Address Test - LANSACCEPT_PHY 2-       | -8          |

|   | 2.2.10.21  | LANCE Force Collision Test — LAN\$COLLISION 2-               |             |

|   | 2.2.10.22  | Receive CRC Logic Test — LANSRCV_GOOD_CRC                    |             |

|   | 2.2.10.23  | Transmit CRC Logic Test — LANSXMT_CRC 2.                     |             |

|   | 2.2.10.24  | Receive Bad CRC Test — LAN\$RCV_BAD_CRC 2.                   | -9          |

|   | 2.2.10.25  | LANCE Broadcast Address and Byte Swap Test — LANSBROADCAST 2 | -9          |

|   | 2.2.10.26  | LANCE Multicast Address Test — LAN\$MULTICAST 2              | -9          |

|   | 2.2.10.27  | External Loopback Test — LANSEXTERNAL_LOOP 2                 | -9          |

|   | 2.2.10.28  | Length, Parity, Initialize Sequence — RT\$CHAR_LENGTH        | -9          |

|   | 2.2.10.29  | DUART Transmit/Receive Break Test — RT\$BREAK 2              | -9          |

|   | 2.2.10.30  | Force Framing Error Test — RT\$FRAMING 2                     | -9          |

|   | 2.2.10.31  | Force Overrun Error, FIFO Depth Check Test — RT\$OVERRUN 2   | -9          |

|   | 2.2.10.32  | Baud Rates Test — RT\$BAUD_RATE 2                            | -9          |

|   | 2.2.10.33  | System Exerciser Test — ST\$EXERCISER                        | -9          |

|   | 2.2.11     | Self-Test Error Codes                                        | 10          |

|   |            |                                                              |             |

| 3 | Initialize | Program                                                      |             |

|   | 3.1        | Introduction 3                                               | -1          |

|   | 3.2        | Down-Line Load                                               | - 1         |

|   | 3.2.1      | Down-Line Load Messages 3                                    | -2          |

|   | 3.2.2      | Down-Line Load Procedure                                     |             |

|   | 3.2.3      |                                                              | 3-3         |

|   | 3.2.4      | •                                                            | 3-3         |

|   | 3.2.5      |                                                              | 3-3         |

|   | 3.3        | • <b>f</b>                                                   | 3-4         |

|   | 3.3.1      | G                                                            | ,<br>3-4    |

|   | 3.3.2      | Nonfatal Errors                                              |             |

|   | = =        | Load Failure or Timeout Error Message                        |             |

|   | 3.3.3      |                                                              |             |

|   | 3.3.4      | Fatal Bugcheck Error Message                                 |             |

|   | 3.3.5      | Timeout, Abort Dump Message                                  |             |

|   | 3.3.6      | Load or Dump Failure Message                                 |             |

|   | 3.3.7      | Bad Image File Message                                       | <b>5-</b> 7 |

|   |            |                                                              |             |

| 4 | On-Line Debugging 1001 (OD I ) |                                                    |  |  |

|---|--------------------------------|----------------------------------------------------|--|--|

|   | 4.1                            | On-Line Debugging Tool                             |  |  |

|   | 4.1.1                          | Initial Requirements 4-1                           |  |  |

|   | 4.1.2                          | Entering ODT 4-1                                   |  |  |

|   | 4.1.2.1                        | Entering ODT from the Self-Test Manufacturing Mode |  |  |

|   | 4.1.2.2                        | Entering ODT from Router Operating Software        |  |  |

|   | 4.2                            | ODT Command Functions 4-2                          |  |  |

|   | 4.2.1                          | Command Input Errors 4-2                           |  |  |

|   | 4.2.2                          | Command Summary 4–2                                |  |  |

|   | 4.3                            | Accessing Router Address Space 4-4                 |  |  |

|   | 4.3.1                          | Memory and Device Register Commands 4-5            |  |  |

|   | 4.3.1.1                        | Examine (E) Command                                |  |  |

|   | 4.3.1.2                        | Examine Byte (EB) Command                          |  |  |

|   | 4.3.1.3                        | Examine Indirect (E@) Command                      |  |  |

|   | 4.3.2                          | CPU Register Commands 4-6                          |  |  |

|   | 4.3.2.1                        | CPU Address Register (\$An) Command 4-6            |  |  |

|   | 4.3.2.2                        | CPU Data Register (\$Dn) Command                   |  |  |

|   | 4.3.2.3                        | CPU Status Register (\$SR) Command                 |  |  |

|   | 4.3.3                          | Dump Commands 4-7                                  |  |  |

|   | 4.3.3.1                        | Memory Dump (D) Command 4-7                        |  |  |

|   | 4.3.3.2                        | Halt Dump (CTRL/C) Command                         |  |  |

|   | 4.3.3.3                        | Register Dump (RD) Command                         |  |  |

|   | 4.4                            | Programming in ODT 4-8                             |  |  |

|   | 4.4.1                          | Program Control Commands 4-8                       |  |  |

|   | 4.4.1.1                        | Go (G) Command 4-8                                 |  |  |

|   | 4.4.1.2                        | Single Step Enable (SS) Command4-8                 |  |  |

|   | 4.4.1.3                        | Single Step Disable (NS) Command 4-9               |  |  |

|   | 4.4.2                          | Breakpoint Commands 4-9                            |  |  |

|   | 4.4.2.1                        | Breakpoint Set (Bn) Command                        |  |  |

|   | 4.4.2.2                        | Breakpoint Clear (BCn) Command                     |  |  |

|   | 4.4.2.3                        | Display Breakpoints (\$B) Command 4-10             |  |  |

|   | 4.4.2.4                        | Breakpoint Message 4-10                            |  |  |

| 5 | Functio                        | onal/Logic Description                             |  |  |

|   | 5.1                            | General 5-i                                        |  |  |

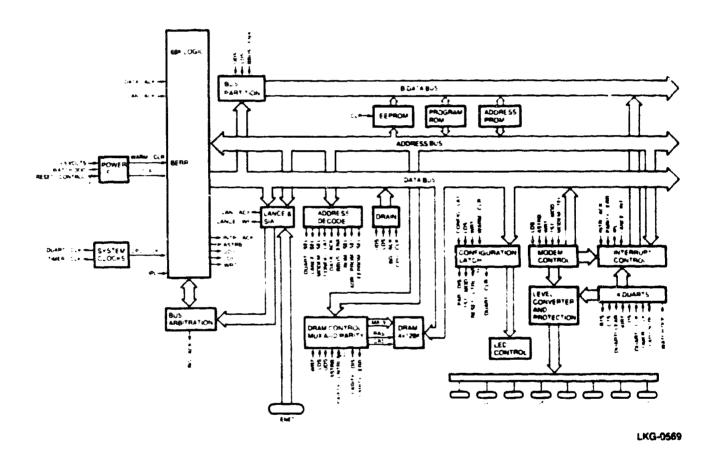

|   | 5.2                            | Microcomputer Logic 5-2                            |  |  |

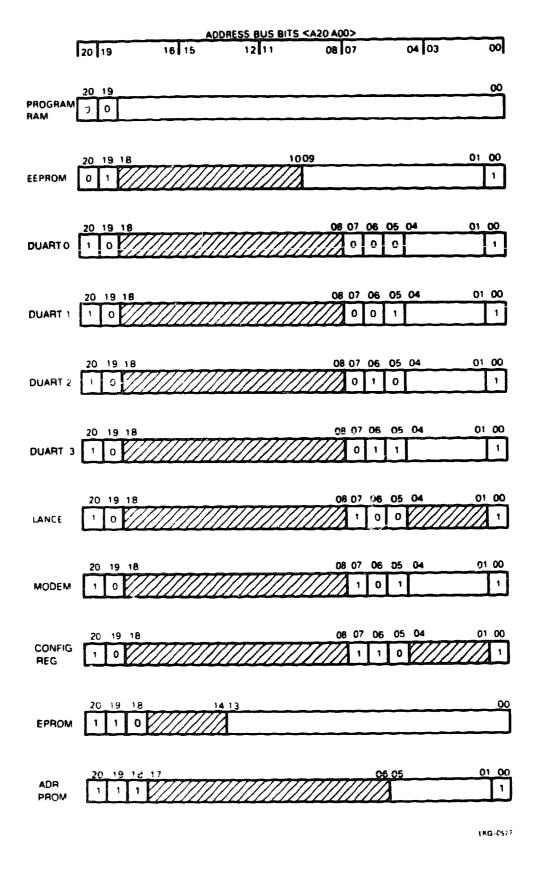

|   | 5.2.1                          | CPU and Data Address Bus 5-2                       |  |  |

|   | 5.2.2                          | Device Addresses 5-2                               |  |  |

|   | 5.2.3                          | CPU and Data/Address Bus Signal Description5-4     |  |  |

|   | 5.2.4                          | Power-Up Sequencer Logic                           |  |  |

|   | 5.2.5                          | Reset Circuitry 5-7                                |  |  |

|   | 5.2.6                          | Warm Reset 5-7                                     |  |  |

|   | 5.2.7                          | Reset Testing                                      |  |  |

|   | 5.2.8                          | System Clock Logic 5-8                             |  |  |

|   | 5.2.9                          | Bus Arbitration Logic                              |  |  |

|   | 5.2.10                         | Interrupt Control                                  |  |  |

|   | 5.2.11                         | Interrupt Vector Addresses                         |  |  |

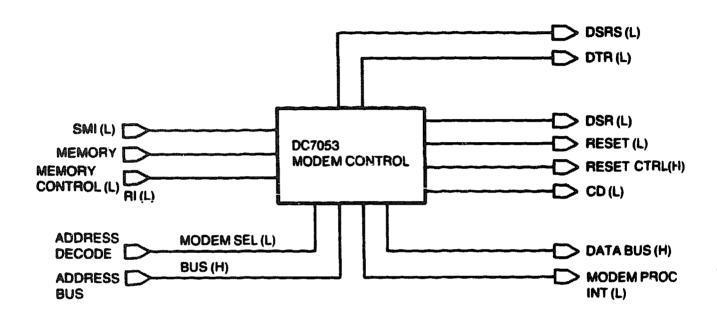

|   | 5.3                            | Modem Control and Interrupts 5-1                   |  |  |

|   | 5.3.1                          | Gate Array (DC7053)                                |  |  |

|   | 5.3.2                          | Register Format for Modern Control Signals         |  |  |

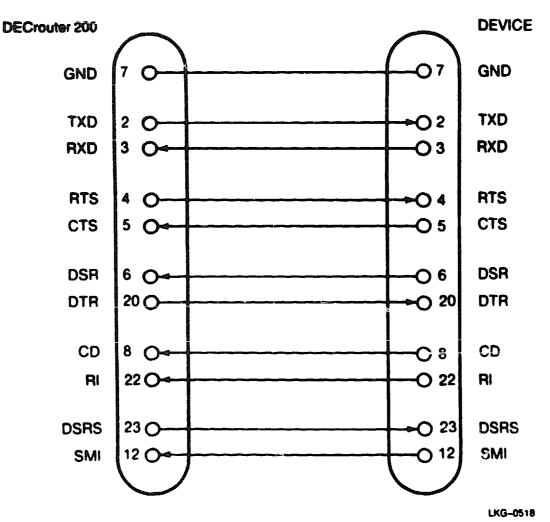

|   | 5.3.3                          | Modem Connection                                   |  |  |

|   | و. و. و                        | 120 CHI COMMECTOR                                  |  |  |

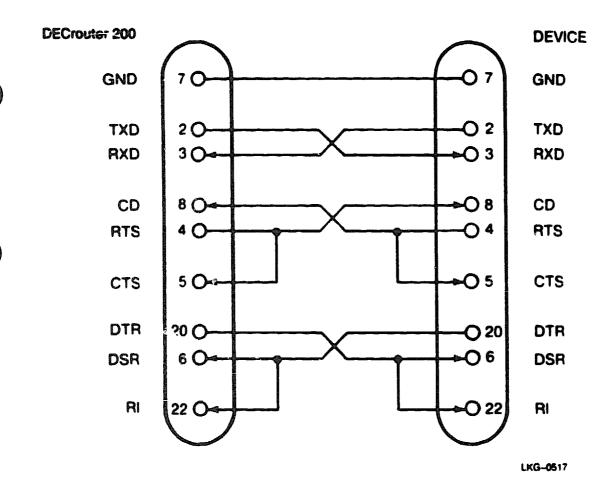

| 5.3.4    | Null Modern Connection                             |        |

|----------|----------------------------------------------------|--------|

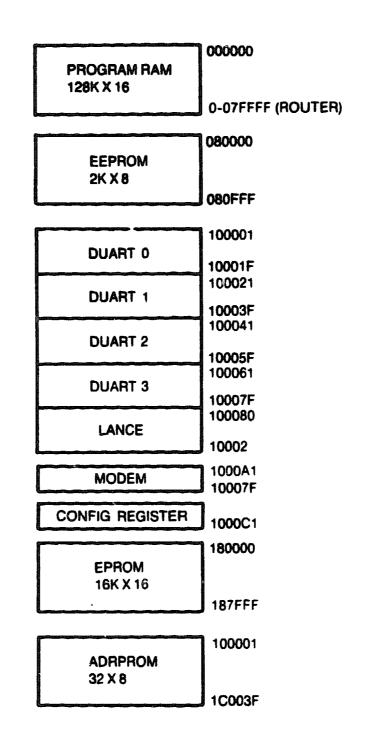

| 5.4      | Router Memory Subsystem                            |        |

| 5.4.1    | Address Selection                                  | 5-18   |

| 5.4.2    | Power-Up Addressing                                | 5-20   |

| 5.4.3    | DUART and LANCE Register Addressing                | 5-21   |

| 5.4.4    | Program Random Access Memory                       | 5-21   |

| 5.4.5    | CPU-Initiated Transfer                             |        |

| 5.4.6    | LANCE-Initiated Transfer                           | 5-21   |

| 5.4.7    | Data Transfer Cycle                                | 5-22   |

| 5.4.8    | Dynamic RAM                                        |        |

| 5.4.9    | Erasable Program ROM (EPROM)                       |        |

| 5.4.10   | Physical Address Programmable ROM (PA PROM)        | 5-23   |

| 5.4.11   | Electrically Erasable Programmable ROM (EEPROM)    | 5-23   |

| 5.4.12   | Write Inhibit                                      |        |

| 5.4.13   | Asynchronous Interface                             |        |

| 5.4.14   | DUART Signal Descriptions                          |        |

| 5.4.15   | Receive and Transmit Registers                     |        |

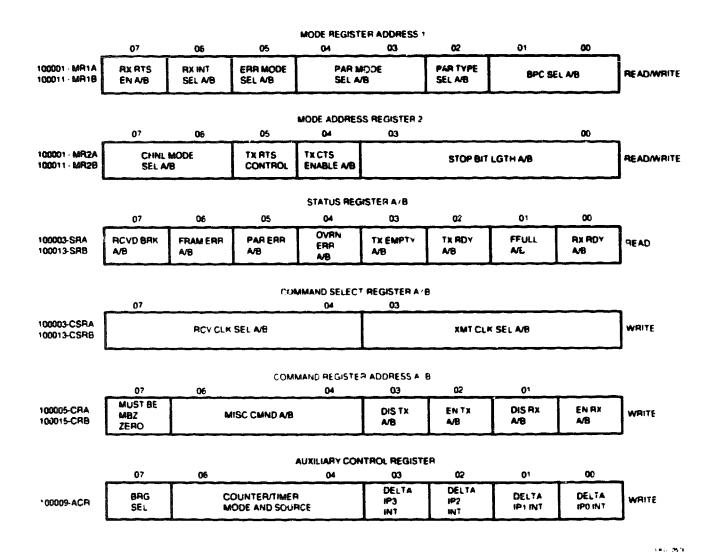

| 5.5      | MRnA and MRnB Mode Registers                       |        |

| 5.5.1    | MR1A and MR1B Bit Assignments                      |        |

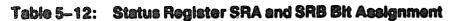

| 5.5.2    | SRA and SRB Status Registers                       |        |

| 5.5.3    | CSRA and CSRB Clock Select Registers               |        |

| 5.5.4    | RHRA and RHRB Receive Holding Registers            |        |

| 5.5.5    | THRA and THRB Transmit Holding Registers           |        |

| 5.5.6    | Auxiliary Control Register ACR < 07 >              |        |

| 5.5.7    | Input and Output Port Registers                    |        |

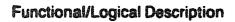

| 5.5.8    | Input Port Change Register (IPCR)                  | 5-35   |

| 5.5.9    | Auxiliary Control Register (ACR < 03:00 > )        |        |

| 5.5.10   | Input Port Status Register (IPSR)                  |        |

| 5.5.11   | Output Port Configuration Register (OPCR)          |        |

| 5.5.12   | Output Port Register (OPR)                         | 5-37   |

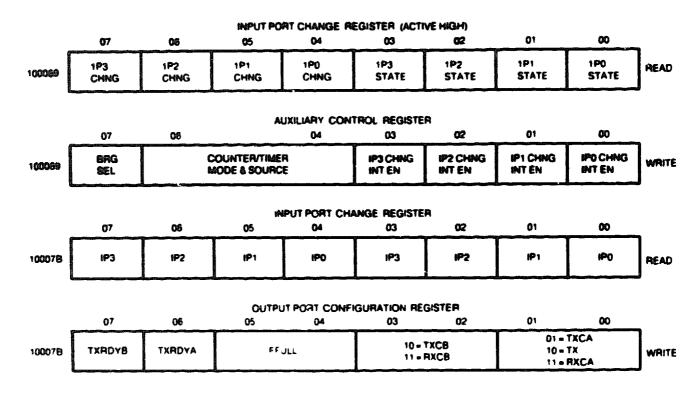

| 5.5.13   | Interrupt Control and Counter/Timer Registers      | 5-37   |

| 5.5.14   | Auxiliary Control Register (ACR < 06:04 >)         | 5-38   |

| 5.5.15   | Interrupt Status Register (ISR)                    | 5-39   |

| 5.5.16   | Interrupt Mask Register                            | 5-40   |

| 5.5.17   | CTUR and CTRL Counter/Timer Registers              |        |

| 5.5.18   | Counter/Timer Start and Stop Commands              |        |

| 5.6      | Ethernet Interface                                 |        |

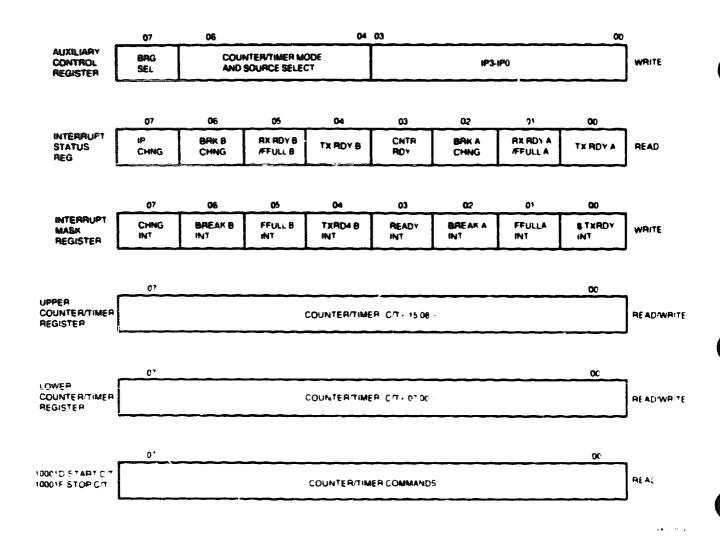

| 5.6.1    | Serial Interface Adapter (SIA)                     |        |

| 5.6.2    | Local Area Network Controller for Ethernet (LANCE) |        |

| 5.6.3    | Ethernet Interface Features                        |        |

| 5.6.3.1  | DMA Transfers with Program RAM                     |        |

| 5.6.4    | Ethernet Operating Modes                           |        |

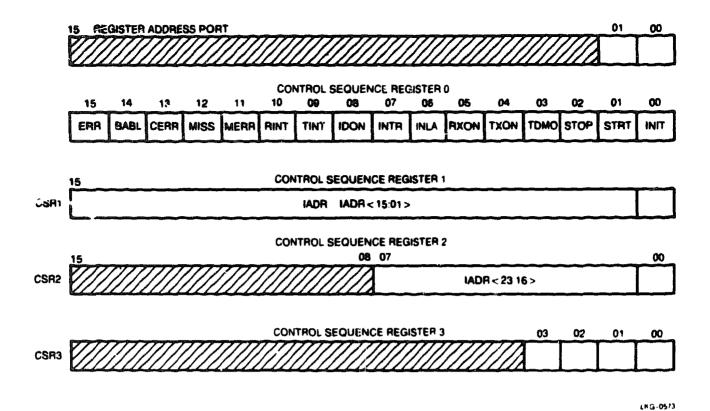

| 5.6.5    | Register Address and Data Ports                    |        |

| 5.6.6    | Register Address Port (RAP) and Latch              |        |

| 5.5.7    | Control/Status Register 0 (CSR0)                   |        |

| 5.6.8    | Control and Status Register 1 (CSR1)               |        |

| 5.6.9    | Control and Status Register 2 (CSR2)               |        |

| 5.6.10   | Control and Status Register 3 (CSR3)               |        |

| 5.6.11   | Buffer Management Protocol                         |        |

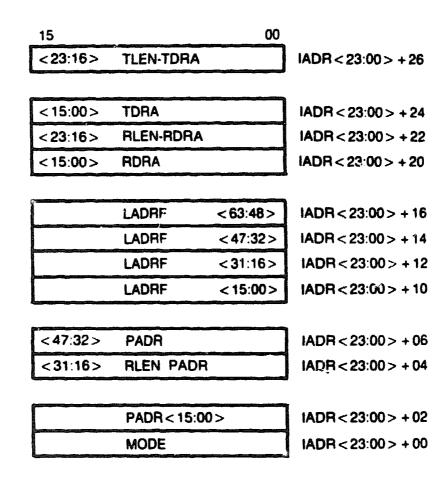

| 5.6.12   | Initialize Block                                   |        |

| 5.6.13   | Mode Register (MODE)                               |        |

| 5.6.14   | Physical Address Register (PADR)                   |        |

| 5.6.14.1 | Logical Address Filter Register (LADRF)            |        |

| 5.6.14.2 | Receive Descriptor Ring Address Register (RDRA)    | . 5-56 |

|         | 5.6.14.3           | Transmit Descriptor Ring Address Register (TDRA)            | 5-56          |

|---------|--------------------|-------------------------------------------------------------|---------------|

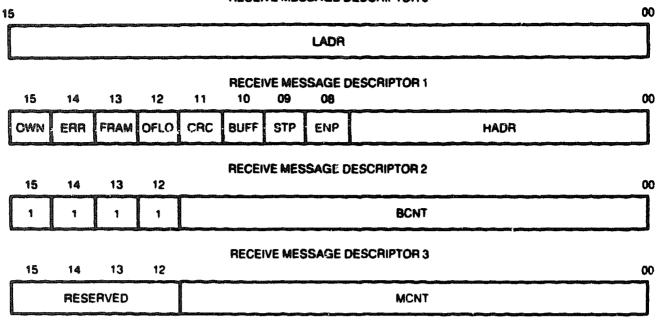

|         | 5.6.15             | Receive Descriptor Ring                                     | 5 <b>-5</b> 7 |

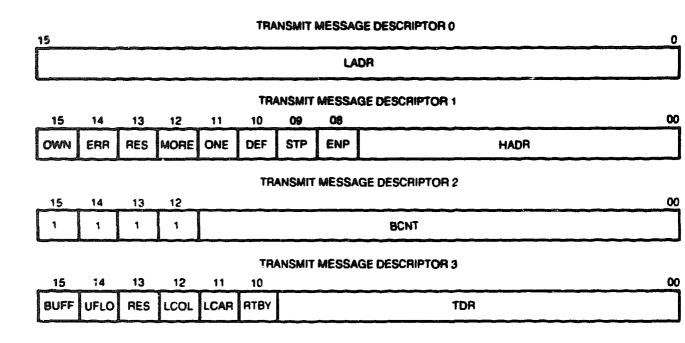

|         | 5.6.16             | Transmit Descriptor Ring                                    | 5–60          |

| 6       | Hardwai            | re Description                                              |               |

|         | 6.1                | General                                                     |               |

|         | 6.2                | Port Devices Supported By DECrouter 200                     |               |

|         | 6.2.1              | Ordering Information                                        |               |

|         | 6.2.2              | DECrouter 200 Country Kits                                  |               |

|         | 6.3                | DECrouter 200 Accessories                                   |               |

|         | 6.4                | Transceiver Cables                                          |               |

|         | 6.5                | Device Cables                                               |               |

|         | 6.6                | DECrouter 200 Specifications                                |               |

|         | 6.6.1              | Power                                                       |               |

|         | 6.6.2              | Environment                                                 |               |

|         | 6.6.2.1            | Temperature                                                 |               |

|         | 6.6.2.2            | Altitude                                                    |               |

|         | 6.6.2.3            | Relative Humidity                                           |               |

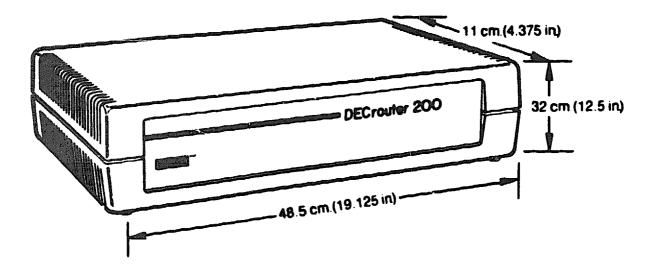

|         | 6.6.2.4<br>6.6.3   | Physical Dimensions of the DECrouter 200 System             |               |

|         | 0.0.5              | space requirements                                          | <b>0-</b> /   |

| Figures |                    |                                                             |               |

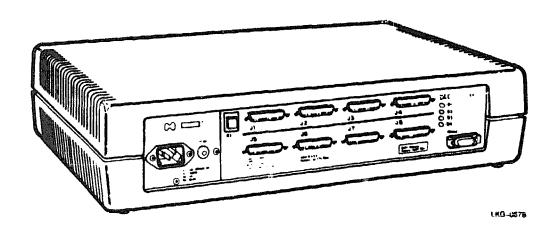

|         | 1-1                | DECrouter 200 Name Panel View                               |               |

|         | 1-2                | DECrouter 200 Cable Connection Panel                        |               |

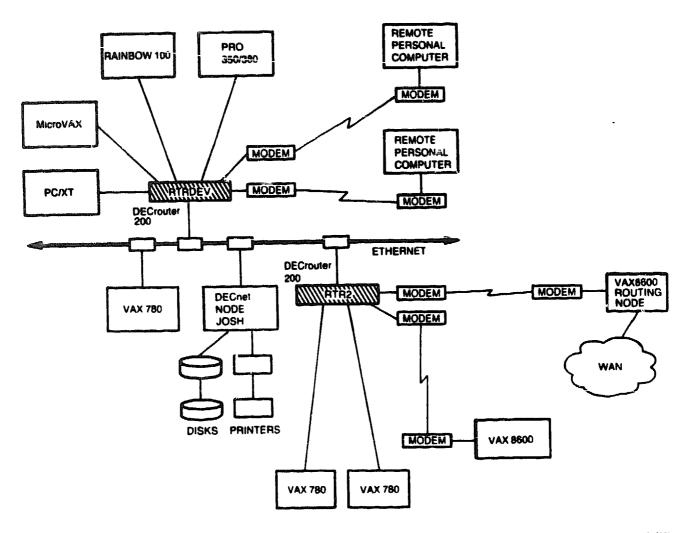

|         | 1-3                | DECrouter in a Large Office/Computer Room Environment       |               |

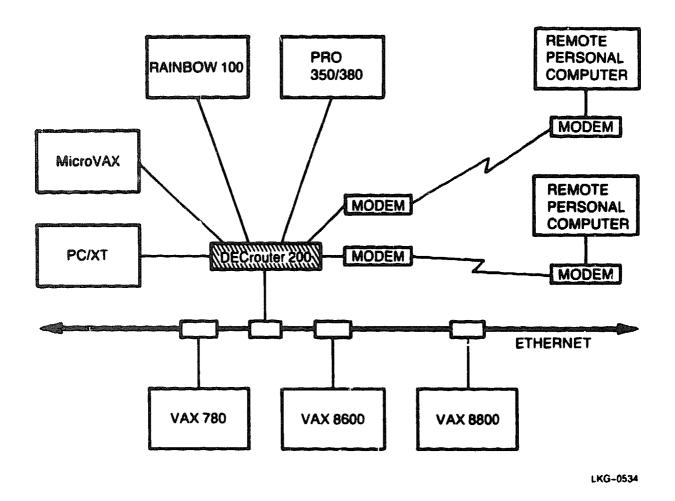

|         | 1-4                | The DECrouter in a Small Office/Computer Room Environment   |               |

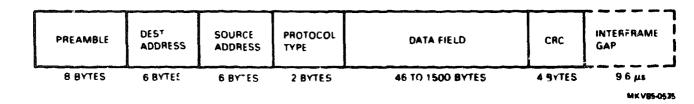

|         | 1-5                | Ethernet Data Frame Format                                  |               |

|         | 5-1                | DECronter 200 Logic                                         |               |

|         | 5-2                | DC705. L'ock Diagram                                        | 5-12          |

|         | 5-3                | DTE-to-DC Hardware Configuration                            |               |

|         | 5-4                | Null Modern Hardware Configuration                          |               |

|         | 5-5                | DECrouter 200 Address Space Allocation                      |               |

|         | 5-6                | CPU Selection of Router Address Space                       |               |

|         | <b>5-</b> 7        | DUART Receive and Transmit Register Formats                 |               |

|         | 5-8                | DUART Input and Output Port Register Bit Settings           |               |

|         | 5-9<br><b>5-10</b> | DUART Interrupt Control and Counter/Timer Register Settings |               |

|         |                    | SIA Connection to an Ethernet Transceiver                   |               |

|         | 5-11<br>5-12       | LANCE Initialize Block Format.                              |               |

|         | 5-12<br>5-13       | LANCE Receive Descriptor Ring Entry                         |               |

|         | 5-14               | LANCE Transmit Descriptor Ring                              |               |

|         | 6-1                | Dimensions of the DECrouter 200 System                      |               |

|         | 0-1                | Difficusions of the Decrouter 200 system                    | 0-0           |

| Tables  |                    |                                                             |               |

|         | 1-1                | Connector Panel Elements                                    | 1-2           |

|         | 1-2                | Ethernet Characteristics                                    |               |

|         | 2-1                | Initialized Mode Parameter Byte                             |               |

|         | 2-2                | Nonfatal Error Longword                                     |               |

| 2-3             | Self-Test Dispatch Table                             | 2-5        |

|-----------------|------------------------------------------------------|------------|

| 2-4             | Self-Test Error Codes                                | 2-10       |

| 3-1             | Router Crash Error Codes                             | 3-6        |

| <b>4</b> -1     | ODT Commands                                         |            |

| <del>1</del> -2 | Router Address Ranges                                | 4-4        |

| 5-1             | Data Strobe Control of Data Bus                      |            |

| 5-2             | Reset Signals and Functions                          | <b>5-7</b> |

| 5-3             | System Clock Functions                               |            |

| 5-4             | Input Modem Register Formats                         |            |

| 5-5             | Output Modern Register Formats                       |            |

| 5-6             | DTE-to-DCE Connection Signals                        |            |

| 5-7             | DTE-to-DTE Connection Signals                        |            |

| 5-8             | Programmable Array Logic Functions                   |            |

| 5-9             | Summary of DUART Register Functions                  |            |

| 5-10            | MRIA and MRIB Bit Assignments                        |            |

| 5-11            | Mode Register MR2A and MR2B Bit Assignments          |            |

| 5-12            | Status Register SRA and SRB Bit Assignment           |            |

| 5-13            | Clock Select Register CSRA and CSRB Bit Assignments  |            |

| 5-14            | Clock Select Registers A and B                       |            |

| 5-15            | Auxiliary Control Register ACR < 07 >                |            |

| 5-16            | IPCR Port Change Register Bit Settings               |            |

| 5-17            | Auxiliary Control Register                           |            |

| 5-18            | Output Port Configuration Register (OPCR)            | 5-36       |

| 5-19            | Auxiliary Control Register ACR < 05:04 >             |            |

| 5-20            | Interrupt Status Register (ISR)                      |            |

| 5-21            | SIA and Ethernet Transceiver Interface Signals       |            |

| 5-22            | LANCE and SIA Interface Signals                      |            |

| 5-23            | LANCE Operating and Data/Address Bus Signals         |            |

| 5-24            | Control and Status Register 0 (CSR0)                 |            |

| 5-25            | Control and Status Register 1 (CSR1)                 |            |

| 5-26            | Control and Status Register 2 (CSR2)                 |            |

| 5-27            | Control and Status Register 3 (CSR3)                 | 5-52       |

| 5-28            | Mode Register Bit Settings                           |            |

| 5-29            | Receive Descriptor Ring Address (RDRA) Bit Settings  |            |

| 5-30            | Transmit Descriptor Ring Address (TDRA) Bit Settings |            |

| 5-31            | Receive Message Descriptor 0 Bit Functions           |            |

| 5-32            | Receive Message Descriptor 1 Bit Functions           |            |

| 5-33            | Receive Message Descriptor 2 Bit Functions           |            |

| 5-34            | Receive Message Descriptor 3 Bit Functions           |            |

| 5-35            | Transmit Message Descriptor 0 Bit Functions          |            |

| 5-36            | Transmit Message Descriptor 1 Bit Functions          |            |

| 5-37            | Transmit Message Descriptor 2 Bit Functions          |            |

| 5-38            | Transmit Message Descriptor 3 Bit Functions          |            |

| 6-1             | DECrouter 200 Hardware Units                         |            |

| 6-2             | DECrouter 200 Country Kits                           |            |

| 6-3             | DECrouter 200 Accessories                            |            |

| 6-A             | DECeputer 200 Power Patient                          | 6_6        |

### **Preface**

The DECrouter 200 Technical Manual provides general operating instructions, detailed hardware logical functions, and diagnostic software information. The DECrouter 200 is also referred to as the router throughout this manual.

### Intended Audience

The manual is for use in training, field service, and manufacturing. The depth of technical information requires previous training or experience with Ethernet networks and with Digital VAX-11 or PDP-11 architecture.

### **Manual Organization**

The manual is divided into the following six chapters:

- **Chapter 1** Introduces the DECrouter 200 and the Ethernet communications system.

- **Chapter 2** Explains the self-test program diagnostic modes and test sequences.

- Chapter 3 Describes how the initialize program handles down-line loading and up-line dumping. Chapter 3 also explains status messages and error messages.

- **Chapter 4** Explains the on-line debugging tool (ODT) commands and how the commands are used.

- **Chapter 5** Provides block diagram level and register address-level descriptions of the DECrouter 200 logic.

- **Chapter 6** Provides lists of router hardware and cable options and the physical and electrical specifications.

### **DECrouter 200 Documents**

- DECrouter 200 Hardware Installation/Owner's Guide

- DECrouter 200 Software Installation Guide (VMS/MicroVMS)

- DECrouter 200 Software Installation Guide (ULTRIX-32/32m)

- DECrouter 200 Management Guide

- DECrouter 200 Identification Card

### **Associated Documents**

- The Ethernet-A Local Area Network-Data Link Layer and Physical Layer Specifications

- Etbernet Installation Guide

- Ethernet Networks: Ethernet Products and Services Catalog

- H4005 Digital Ethernet Transceiver Installation Manual

- H4005 Digital Ethernet Transceiver Technical Manual

- DELNI Installation/Owner Manual

- Installing Etherjack

- Motorola Microprocessor Data Manual

- Routing and Networking Overview

## DECrouter 200

### 1.1 DECrouter 200 Introduction

The DECrouter 200 system is an Ethernet-based device that allows network connection for up to eight asynchronous devices. The primary use for the router is to connect IBM personal computer nodes running DECnet-DOS, specifically, the IBM Personal Computer/AT and the IBM PC/XT, to the Ethernet and to wider DECnet networks, using existing office wiring. The router also connects the Digital Rainbow 100 series, and the Digital Professional 300 series of personal computers to the Ethernet and wider area networks, using existing office wiring. The DECrouter 200 also connects any DECnet nodes using asynchronous DDCMP with or without modem control. DECrouter 200 has two interfacing capabilities: from devices or dial-in modems to the Ethernet; or from computer systems or dial-out modems to the Ethernet. Figure 1–1 shows the name panel of the router.

Figure 1-1: DECrouter 200 Name Panel View

### 1.1.1 Firmwere

Two kilobytes of EEPROM store all terminal default parameters and some system default parameters for each communication line. The EEPROM has a limited life of 10,000 write cycles per byte and must be protected from indiscriminate write cycles. Write cycles, which are signaled by an enable bit to the EEPROM, permit a single write cycle, and are only read by the router ROM code. For a detailed description of EEPROM and its functions, see Sections 5.4.11 and 5.4.12.

### 1.1.2 Programmable Timers

Four 2681 communications dual asynchronous receiver transmitters (DUARTs) provide four 16-bit timers (DUARTs 0-3) with the following functions:

- DUARTO Processor interrupt timer for dynamic memory refresh

- DUART 1 General purpose timer/set to 25 milliseconds

- DUART2 Watchdog timer for fatal (hard) errors

- DUART3 Timer for LED status indicators

For a detailed description of programmable timers, see Sections 5.5.13 through 5.5.18.

### 1.2 Ethernet Interface System

The hardware interface between the DECrouter 200 and the Ethernet is controlled through a chip set consisting of a Local Area Network Controller for Ethernet (LANCE) and a Serial Interface Adapter (SIA). The chip set converts Manchester encoded serial data at 10 Mbits per second into parallel, 16-bit data for memory storage.

### 1.2.1 Local Area Network Controller for Ethernet (LANCE)

The LANCE is a master/slave, direct memory access (DMA) device that converts 10 MHz of serial data into 16-bit words of parallel data. The LANCE, in slave mode, allows direct memory access from the 68000 data bus. For a detailed description of the LANCE, see Section 5.6.2.

### 1.2.2 Serial Interface Adapter (SIA)

The SIA is a Manchester encoder/decoder with IEEE and Ethernet specifications. The SIA links the LANCE to the Ethernet transceiver cable and acquires clock signals and data from the Manchester output at 10 MHz. For a detailed description of the SIA, see Section 5.6.1.

#### 1.2.3 Service Node and Load Host

Processors supporting the DECrouter 200 on an Ethernet system provide service nodes that:

- Implement DECnet Phase IV software

- Serve as load hosts to down-line load the DECrouter software image to any requesting router

### 1.2.4 Firmware and Software

Following is a list of the Programmable Read Only Memory (PROM) code on the DECrouter 200 printed circuit board:

- Self-test program

- Initialize program down-line loading and up-line dumping

- On-line debugging tool (ODT)

- Upon power-up, the Self-test program performs a series of diagnostics and signals for the initialize program.

- The initialize program signals a request for a down-line load, based on the router physical

- The DECrouter then loads from the first properly configured Phase IV DECnet system that responds to the request.

- When loaded, the router software operates until the next power-up sequence. When the router parameters are properly set, data can be routed between nodes on the Ethernet and nodes connected to asynchronous ports.

### 1.3 Connector Panel Element Description

### 1.3.1 Controls and Connectors

Figure 1-2 is a view of the router showing cable connectors, switches, and LEDs. The information in Table 1-1 explains the function of each LED.

### Table 1-1: Connector Panel Elements

The four LEDs on the back of the router function as follows:

|                 | State    | Condition                           |

|-----------------|----------|-------------------------------------|

| Power — D1      | ON       | DC voltage OK 5V power              |

|                 | OFF      | DC voltage problem 5V power         |

| Diagnostic — D2 | ON       | Selftest OK                         |

| C,              | OFF      | Fatal error or test in progress     |

|                 | BLINKING | Non-fatal (soft) error              |

| Software — D3   | ON       | Operating software loaded, no error |

|                 | OFF      | Down-line load in progress          |

|                 | BLINKING | Loading failed, will-try-again      |

| Ethernet        | ON       | Network active                      |

| Carrier — D4    | OFF      | Network not active                  |

#### NOTE

Soft errors do not hinder minimum operation of the system. Hard errors hinder overall operation of the system. The software LED is only valid when the diagnostics are done.

DECrouter 200

### 1.3.2 Switch \$1

The switch is not functional on the router.

Figure 1-2: DECrouter 200 Cable Connection Panel

### 1.3.3 Asynchronous Ports (J1 - J8)

Through the eight 25-pin male connectors, the router can accommodate up to eight personal computers or any computer systems that have asynchronous DDCMP protocol. Chapter 6 contains a complete list of standards and protocols for interfacing serial lines and the Ethernet.

### 1.3.4 Ethernet Transceiver Port

The Ethernet transceiver connector, a 15-pin female type, is on the bottom right corner of the rear panel. The device connects the router to a Digital Ether let transceiver or a DELNI transceiver cable.

### 1.3.5 AC Line Voltage Input Selector Switch

The line voltage input selector switch is to the right of the AC power receptacle. The switch allows the installer to set the router for 47-63 Hz input speed as follows:

- 120 Vac, 90 Vrms to 128 Vrms, single phase, 3-wire

- 240 Vac, 176 Vrms to 268 Vrms, single phase, 3-wire

### 1.3.6 AC Power Cord Receptacle

A country-specific power cord is supplied with the router.

### 1.3.7 AC Circuit Breaker

The server has a resettable circuit breaker to the right of the power receptacle on the rear of the server.

### 1.3.8 Power-Up and Initialization

After installation and power application, a terminal can be plugged into J1 to check for Self-test error messages or for down-line load messages. The terminal must be set to the following default characteristics:

- Transmit/Receive = 9600

- Character size = 8 bits

- Parity = None

### 1.3.9 Initialization Sequence

Application of an AC power source initiates the following power-up sequence:

- 1. The power LED lights.

- 2. Self-test begins, and if no soft errors are detected, the Self-test LED lights.

- 3. The down-line code is invoked and the router software image is down-line loaded. After successful down-line loading, LED2 lights.

- 4. The router image begins execution.

- 5. The unit is functioning.

### 1.4 Ethernet Systems

The Ethernet, as a local area network (LAN), is a communication method based on joint specifications from Digital, Intel Corporation, and Xerox Corporation. For extensive hardware descriptions, refer to The Ethernet – A Local Area Network – Data Link Layer and Physical Layer Specification.

The LAN communication system supports a 10-MHz data rate over interconnected coaxial cables. The Ethernet specification defines the physical properties of the coaxial cable, the transceiver, and some of the peripheral hardware. The specification also defines basic rules for network access, device addressing, and data frame format.

### 1.4.1 System Elements

Figure 1-3 shows the DECrouter used in a large office and computer room environment. DECrouter 200 RTRDEV in Figure 1-3 offers:

- Connection to personal computers

- Connection using existing twisted-pair wiring

- Modems in office area accessing remote personal computers

DECrouter 200 RTR2 in Figure 1-3 offers:

- Connection to large DECnet systems

- Modern connections to remote facilities

- Modems in a computer room for access to the network by remote nodes

LKG-0535

### Figure 1-3: DECrouter in a Large Office/Computer Room Environment

Figure 1-4 shows a DECrouter 200 used in a small office environment to connect a few workstations to an office computer. The configuration shows personal computers used as workstations connected to a network that uses a DELNI as the Ethernet.

**DECrouter 200**

Figure 1-4: The DECrouter in a Small Office/Computer Room Environment

### 1.4.2 Configuration Criteria

Following are the configuration criteria for optimum network performance on an Ethernet:

- Each coaxial cable segment can be any length up to 500 meters (1640 feet) and must be terminated at both ends at 50 ohms impedance.

- A maximum of 100 stations can be installed on a single cable length. Transceivers must be at least 2.5 meters (8.2 feet) apart.

- Transceiver cables can be any length up to 50 meters (164 feet).

- A repeater can extend the system by connecting two coaxial cable segments through two transceivers.

- The network can be extended using two remote repeaters with an optical point-to-point link of up to 1,000 meters (3,281 feet) as shown in Figure 1-5.

- A maximum of two repeater or remote repeater combinations can be used between any two points on the system.

- A maximum of 1,024 stations can be connected to an extended network. Such a network must be configured with no more than 2.80 km (1.74 miles) separating any two stations on the network, including point-to-point links and transceiver cables.

### 1.4.3 Communications Methods

Ethernet uses a branching bus topology with a coaxial cable as the transmission medium. Each station transmits a preamble at its start. Receiving stations synchronize and acquire timing from the preamble. The preamble information reduces problems with line skew or variations in carrier frequency. During transmission, a station calculates a cyclic redundancy check (CRC) value, which is appended to the end of the transmission.

### 1.4.4 Network Access and Communication Protocol

The router supplies power to the Ethernet transceiver on one twisted pair of transceiver cable. Communications between the router and the transceiver are on the following signal pairs:

- Transmit pair The routez encodes and sends Manchester serial data on the transmit pair.

- Receive pair The router receives Manchester-encoded serial data on the receive pair.

### NOTE

The router, operating in half-duplex mode, must be in either transmit mode or receive mode at a given time. When the router is receiving data, the transceiver monitors the coaxial cable for signals and reports the start of a transmission.

Collision pair — The transceiver reports a collision condition with another station by sending a

10-MHz carrier to the router on the collision pair. The transceiver also tests for router collision

detection circuits by sen and 10-MHz frequency for approximately 2 microseconds after every

transmission. This is called a heartbeat check.

### 1.4.5 Network Access

There is no priority arbitration for access to an Ethernet. All systems and nodes have equal access Access is gained using a line contention/collision detection protocol called Carrier Sense Multiple Access with Collision Detection (CSMA/CD).

### 1.4.6 Collision Detection

Two or more stations transmitting at once nets a collision, which destroys data. When a collision is detected, the transmitting stations continue transmission for a predetermined time. The continuation of transmission is detected by all stations on the network.

DECrouter 200 1–9

Following are frequently used collision detection terms:

- Deference When a collision is detected, all transmitting stations, and/or stations waiting to transmit, wait for an integral number of slot times, which are determined by an exponential binary backoff algorithm, before trying to transmit again. Each subsequent collision and backoff reduces the possibility of further collisions. This way all stations gain access at random intervals and can complete transmissions.

- Slot Time The maximum time, 51.2 microseconds, in which collisions are apt to occur on a network. Slot time represents the maximum time from when a station starts to transmit to the time that it detects a collision with another transmitting station on the network. Any collision detected beyond 51.2 microseconds is flagged as a late collision error.

- Collision Circuitry Test (Heartbeat) For the transceiver: Tests the router collision detection circuitry by sending a 10-MHz frequency load for approximately 2 microseconds after a normal transmission. A collision circuit failure is recorded as a nonfatal hardware error.

### 1.4.7 Data Frame Format

Each station transmits a frame of serial data in the format shown in Figure 1-5. Each data-byte is right-shifted within the format.

Figure 1-5: Ethernet Data Frame Format

### Table 1-2: Ethernet Characteristics

| Characteristic                 | Value/Definition                                                                       |

|--------------------------------|----------------------------------------------------------------------------------------|

| Topology                       | Branching bus                                                                          |

| Transmission Medium            | Coaxial cable using Manchester-encoded digital baseband signaling                      |

| Data Rate                      | 10 million bits per second (10 MHz)                                                    |

| Maximum Separation of Stations | 2.80 km (1.74 miles)                                                                   |

| Maximum Number of Stations     | 1,024 stations                                                                         |

| Network Control                | Multi-access with equal distribution to all stations                                   |

| Access Control                 | Carrier sense multiple access with collision detection (CSMA/CD)                       |

| Data Frame Format              | 72 to 1526 bytes, including a preamble, with a variable data field of 46 to 1500 bytes |

The following list identifies and describes each of the seven Ethernet data frame fields.

- 1. Proamble A 64-bit (8-byte) pattern of alternating 1s and 0s that allows the receiver circuits to settle. The last two bits are transmitted as 1s for synchronization, indicating that all following information is interpreted as data.

- 2. Destination Address A 48-bit (6-byte) address that specifies the destination station. Each station has a unique Ethernet address and examines the field to determine if it should accept or reject the data frame.

- If the high order bit of the first byte is a 0, the destination address is unique to each particular station. If the high order bit is a 1, a logical group of recipients or devices can be specified in a multicast address. A broadcast address of all 1s indicates that all stations on the network are to accept the data frame.

- 3. Source Address 2 48-bit (6-byte) address that identifies the transmitting station.

- 4. Protocol Type A 16-bit (2-byte) code that identifies the client layer protocol associated with the frame when multiple higher level protocols are sharing the network. Protocol type is not interpreted at the Data Link layer.

- 5. Data Field The data field can have from 46 to 1500 bytes. The 46-byte minimum ensures that all recipients are able to recognize valid data frames and discard smaller sequences as collision fragments.

- 6. Cyclic Redundancy Check (CRC) A CRC-16 calculation performed on all fields except the preamble and appended to the end of the frame.

- 7. Interframe Gap Every station must supply an interframe gap of at least 9.6 microseconds on a multiple-frame transmission.

### 1.4.8 Ethernet Characteristics

The information in Table 1-2 explains the major characteristics of an Ethernet system.

DECrouter 200 1–11

### 2 Self-Test

### 2.1 General

This chapter describes the Self-test diagnostics residing in PROM. Self-test can operate in one of four modes:

- Normal Mode

- Manufacturing Mode

- Initialized Mode

- Fatal Error Mode

Normal Mode, Manufacturing Mode, and Initialized Mode test router hardware. Fatal Error Mode reports fatal router errors.

### 2.2 Self-Test Operating Modes

### 2.2.1 Normal Mode

The diagnostic mode under which Self-test typically runs, for example at a customer site, is called Normal Mode operation.

Self-test starts when power is applied to the router. When no fatal errors are detected, Self-test signals, lighting D2, and transfers control to the router firmware. In Normal Mode, Self-test executes in less than 15 seconds.

The primary indication for a fatal error is that D2 does not light. When a fatal error is detected, Selftest enters Fatal Error Mode.

### 2.2.2 Manufacturing Mode

Self-test checks whether or not the Manufacturing Mode jumper is connected. If the jumper is connected, the following changes occur in the test modes:

The Self-test program loops continually.

### NOTE

D2 lights after the first successful pass of Self-test, and remains on as the program loops, until a fatal error is detected.

- Dynamic memory is more extensively tested.

- The Ethernet port and all terminal ports are tested in the external loopback mode.

- Due to a limited life of approximately 10 K writes per byte, the read/write tests of EEPROM are disabled after the first pass.

- All errors are fatal, causing Self-test to turn off D2 and halt execution.

- Self-test executes in less than 35 seconds.

Manufacturing mode is terminated by removing the jumper and recycling power to the router.

### 2.2.3 Initialized Mode

Initialized Mode is entered from the router software when Self-test is called by the INITIALIZE command in Privileged Local Mode. Initialization control information is saved, and the Self-test parameters are used or changed as needed. Self-test is accessible from the Load/Dump microcode after an unsuccessful load.

In entry mode, the upper 256 bytes of RAM contain the router data called Initialized-RAM. Initialized Mode starts at the first test module and operates under the parameters specified in the Initialized Mode Parameter Byte. Self-test execution time depends on the parameters specified in this byte. Table 2–1 describes the information in the Initialized Mode Parameter Byte.

Table 2-1: Initialized Mode Parameter Byte

| Bits                  | Mode Name | Test Description                                                                             |  |

|-----------------------|-----------|----------------------------------------------------------------------------------------------|--|

| <07>                  | Long      | When set, enables the extended RAM test                                                      |  |

| <02:00> LOOP MODE $n$ |           | Select one or a combination of the following test modes:                                     |  |

|                       | Bit       | Test Mode Selection                                                                          |  |

|                       | <00>      | Loop Self-test — Enables the self-test to loop on itself for a specified number of passes    |  |

|                       | <01>      | External Loopback Terminal — Enables external loopback tests of the terminal ports           |  |

|                       | <02>      | Disable NI External Loopback — Disables external loopback tes .ng of the LANCE and SIA chips |  |

### 2.2.4 Fatal Error Mode

Self-test enters Fatal Error Mode when a fatal error is detected. All errors are fatal in Manufacturing Mode.

The error routine writes the test it error to a byte location in EEPROM and is cleared by the power-up reset procedure.

### 2.2.5 Error Types

Errors detected by Self-test are classified as either nonfatal or fatal:

- Nontatal errors are failures that interfere with normal operation or cause the router to operate at decreased capacity. At completion, Self-test causes D2 to blink if a nonfatal error is detected. The error status parameter is written to Initialized-RAM, and identifies the error for evaluation by the router software.

- Fatal errors can disable the router or cause erratic operation. For fatal errors, D2 remains off and error mode is entered. Unexpected traps and all Manufacturing Mode failures are fatal or "hard" errors.

### 2.2.6 Nonfatal Errors

The following list explains nonfatal errors:

- **EEPROM Checksum Error** EEPROM is divided into several functional areas with a parameter checksum maintained in each area. Bad data in any or all of these areas are considered nonfatal.

- LANCE Error (heartbeat or external loopback error) When Self-test detects an error while testing the LANCE in external loopback mode, it flags the nonfatal error in the status longword. The external loopback test is disabled by selecting the internal loopback mode in the Initialized Mode Parameter Byte.

- Asynchronous Port Errors (on usable ports) Self-test flags port errors to the router firmware in the status longword. Router software disables ports after a down-line load. If errors are detected on all eight ports, the router is not usable. This is a fatal error condition.

- Modem Control Signal Error Indicates a modem control signal error on one or more ports.

#### 2.2.7 Nonfatal Error Status

Two nonfatal status longwords are written to Initialized-RAM, in the upper 256 bytes of RAM, by Self-test. The first longword contains the EEPROM checksum error status.

The router has 2 K-bytes of EEPROM. There is a checksum field in each of the 22 sections of EEPROM. Sections are divided as follows:

- Router parameters that contain 173 bytes in 1 section

- Diagnostics that contain 20 bytes in 1 section

- Hardware revisions that contain 3 bytes in 1 section

Self-Test 2–3

- Port parameters that contain 1120 bytes in 8 sections

- Service parameters that contain 700 bytes in 10 sections

- Encryption parameters in 1 section

In normal mode, checksum errors are nonfatal. A checksum error is indicated when any one of the following bits is set:

| 0 | Bit < 00>     | Checksum error in the router parameter section     |

|---|---------------|----------------------------------------------------|

| 9 | Bit < 01 >    | Checksum error in the diagnostic section           |

| 0 | Bit < 02 >    | Checksum error in the hardware revision section    |

| 0 | Bit < 10:03 > | Checksum error in the port parameter sections      |

| 8 | Bit < 20:11>  | Checksum error in the service parameter sections   |

| 0 | Bit < 21>     | Checksum error in the encryption parameter section |

### NOTE

When no fatal errors are detected in Self-test, the two longwords are returned to the load/dump microcode. The following table gives the mnemonic and the function of each bit in the second nonfatal error status longword.

Table 2-2: Nonfatal Error Longword

| Bit     | Mnemonic | Function                                                                                                                                                                                                                                                                                                      |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <18>    | RTF      | Reset to Factory is a status bit; when set, it indicates that the contents of EEPROM was reset to the factory default parameters.                                                                                                                                                                             |

| <17>    | NI       | Network Interconnect indicates a heartbeat error was detected while operating the LANCE.                                                                                                                                                                                                                      |

| < 16 >  | XLB      | This indicates that the External Loopback Test has failed.                                                                                                                                                                                                                                                    |

| <15:08> | MCS      | Modem Control Self-test indicates that the modem control hardware on a channel has failed Self-test. In the longword there is a bit for each channel, which is set if the channel fails. MCS errors are always nonfatal because the router always operates when the data leads on the channel still function. |

| <07:00> | CHAN     | Channel Failure; when bit 2 in the longword is set, channel 2 failed Self-test. CHAN errors are nonfatal if at least one channel functions. Failure of all eight channels to pass Self-test indicates a fatal error.                                                                                          |

### 2.2.8 Fatal (Hard) Errors

All errors that are not considered nonfatal, are fatal. Following are some typical fatal errors:

- Program RAM Data Error Any program RAM data error detected by any memory test

- Program ROM Cyclic Redundancy Check (CRC) Error An error detected on the CRC calculation of the PROM

- Timer Error Any failure detected by the refresh or watchdog timer tests

- LANCE Error Any error detected during initialization or on an internal loopback operating test

- Terminal Port Error When no terminal ports are usable, leaving the router inoperable

### 2.2.9 Using the Diagnostic LED (D2)

Self-test indicates its status using D2. After executing, Self-test leaves D2 in one of three states: ON, OFF, or BLINKING.

- D2 ON Self-test has completed without detecting any hardware errors.

- D2 OFF A fatal hardware error was detected.

- D2 BLINKING A nonfatal hardware error was detected; an error message displays on the console terminal. See the *DECrouter 200 Management Guide* for a complete description of the diagnostic error messages.

In Normal Mode, Self-test executes in under 15 seconds. In Manufacturing Mode, it takes at least 35 seconds. In Initialized Mode, the execution time varies according to the parameters selected in the Initialized Mode Parameter Byte.

### 2.2.10 Self-Test Program Tests

There is one loop that calls each test, in order. After a test is run, the test returns to the loop. Tests are executed from both RAM and ROM.

Following is the dispatch table, which shows each test by number. The table also shows how each test is invoked, where the test executes, and the test name:

Table 2-3: Self-Test Dispatch Table

| Test | Invoked by | Execution | Name                   |

|------|------------|-----------|------------------------|

| 01   | Jump       | ROM       | ST\$CPU REG J          |

| 02   | Jump       | ROM       | ST\$JAM TEST J         |

| 03   | Jump       | ROM       | ST\$QUICK RAMJ         |

| 04   | Jump       | ROM       | ST\$EXTENDED RAM J     |

| 05   | Jump       | ROM       | ST\$STUCK INTERRUPTS J |

(continued on next page)

Self-Test 2-5

Table 2-3 (cont.): Self-Test Dispatch Table

| Test | Invoked by | Execution | Name                 |

|------|------------|-----------|----------------------|

| 06   | Cail       | ROM       | ST\$REFRESH TIMER    |

| 07   | Call       | ROM       | LANSREG TEST         |

| 08   | Jump       | ROM       | ST\$WD TIMER         |

| 09   | Call       | ROM       | ST&GP TIMER          |

| 10   | Call       | ROM       | ST\$LOADER           |

| 11   | Call       | ROM       | ST&PROM CRC          |

| 12   | Call       | ROM       | ST\$NI ADDRESS       |

| 13   | Call       | ROM       | ST\$PARITY           |

| 14   | Call       | ROM       | STSEEPROM RW         |

| 15   | Call       | ROM       | ST\$RESET TO FACTORY |

| 16   | Call       | ROM       | STSEEPROM CS         |

| 17   | Cali       | ROM       | ST\$MODEM CS         |

| 18   | Call       | ROM       | ST\$RTS CTS          |

| 21   | Call       | RAM       | LAN\$REJECT          |

| 22   | Call       | RAM       | LANSACCEPT PHY       |

| 23   | Call       | RAM       | LANS COLLISION       |

| 24   | Call       | RAM       | LAN\$RCV GOOD CRC    |

| 25   | Call       | RAM       | LAN\$XMT CRC         |

| 26   | Cail       | RAM       | LANSRCV BAD CRC      |

| 2~   | Call       | RAM       | LAN\$BROADCAST       |

| 28   | Call       | RAM       | LAN\$MULTICAST       |

| 29   | Call       | RAM       | LANSEXTERNAL LOOP    |

| 30   | Call       | RAM       | RT\$CHAR LENGTH      |

| 31   | Call       | RAM       | RT#BREAK             |

| 32   | Call       | RAM       | RT\$FRAMING          |

| 33   | Call       | RAM       | RT\$OVERRUN          |

| 34   | Call       | RAM       | RT\$BAUD RATE        |

| 38   | Call       | RAM       | STSEXERCISER         |

- 2.2.10.1 Processor Register Test STSCPU\_REG\_J Verifies that there are no stuck-at faults in the CPU registers.

- 2.2.10.2 Self-Test UN-JAM Test STSJAM\_TEST\_J Verifies that the reset state is cleared. When the router is powered up, the hardware reset signal causes PROM to map to a RAM address space where the CPU fetches its reset vectors and starts execution. Clearing the reset allows the mapping of PROM to its correct address.

- 2.2.10.3 RAM Quick Verify Test ST\$QUICK\_RAM\_J Verifies that each RAM location is addressable and that no locations have stuck-at faults. The algorithm also yields full coverage of shorted or open address lines.

- 2.2.10.4 Extended RAM Test STSEXTENDED\_RAM\_J Provides extensive Program RAM tests; the test executes only when in Manufacturing Mode, or when called from LAT software with extensive memory testing enabled. This test identifies stuck-at faults and coupling faults, and ensures that all calls exist.

- 2.2.10.5 Stuck-at Interrupt Test ST\$STUCK\_INTERRUPTS\_J Verifies that no processor interrupts are pending. Processor interrupts can be caused by malfunctioning interrupt logic.

- 2.2.10.6 Refresh Timer Test ST\$REFRESH\_TIMER Verifies that the refresh timer (DUAR 10) interrupts at the correct Interrupt Priority Level (IPL) and the correct vector, and that the timer is running in free running mode.

- 2.2.10.7 LANCE Register Test LANSREG\_TEST Verifies that the CPU correctly accesses the LANCE registers, and ensures that there are no stuck-at faults in the LANCE registers, and that the LANCE is correctly reset.

- 2.2.10.8 Watchdog Timer Test ST\$WD\_TIMER Ensures that the Watchdog Timer resets the module. This function of the Watchdog Timer is tested only on the first pass of Self-test; subsequent passes check whether or not the watchdog timer expires. Resetting of the module is not allowed. Before exiting, the watchdog subsystem is initialized, so that when any portion of Self-test hangs, the timer expires, causing a fatal error.

- 2.2.10.9 General Purpose Timer Test ST\$GP\_TIMER Verifies that the general purpose timer (DUART1) interrupts at the correct IPL and that the timer and the correct vector, and that the timer is in free running mode.

- 2.2.10.10 Test Loader ST\$LOADER To simulate normal router operation, several tests execute in RAM rather than in PROM. The ST\$LOADER test copies these tests to RAM and verifies that they were correctly copied.

- 2.2.10.11 PROM CRC Test ST\$PROM\_CRC Performs a Cyclic Redundancy Check (CRC) on the entire contents of the PROM; compares PROM contents with the value CRC stored in the last longword of the PROM.

- 2.2.10.12 NI Address PROM Checksum Test ST\$NI\_ADDRESS Performs a checksum calculation on the 32-byte NI Address PROM that holds the router Ethernet address and compares the result with the checksum stored in the PROM.

- 2.2.10.13 Parity Logic Test ST\$PARITY Ensures that the parity logic correctly detects and reports various parity errors.

- 2.2.10.14 EEPROM Psad/Write Test STSEEPROM\_RW Verifies the read and write functions of EEPROM and tests the write-enable and write-disable logic. EEPROM has a limited life cycle, and writes to the area should be used discriminately. Looping on the portion of the test that writes to EEPROM is not allowed.

Self-Test 2–7

2.2.10.15 Reset to Factory Test — ST\$RESET\_TO\_FACTORY — During power-up, when all the LEDs are on, the reset switch (S1) is polled. A flag is set true if the reset switch is pressed during a .5-second interval. This test examines the flag and, if true, the remainder of the test executes.

The contents of EEPROM are restored to its factory default settings. Default parameters in ROM are copied to the EEPROM, and new checksum calculations are performed and included in EEPROM.

- 2.2.10.16 EEPROM Checksum Test STSEEPROM\_CS EEPROM is divided into these sections:

- Router parameters

- LANCE, ECO, and revision parameters

- Diagnostic parameters

- Separate areas for each of the eight terminal ports

This test verifies the accuracy of all but the diagnostic parameter section of EEPROM.

- 2.2.10.17 Modem Control Signals Test ST\$MODEM\_CS Checks modem control signal logic, ensuring that each bit in every modem control register can be set and cleared; tests each change-detect and interrupt generation circuit for proper functioning.

- **2.2.10.18** Request-to-Send Test ST\$RTS\_CTS Verifies that the request-to-send and clear-to-send flow control logic functions properly.

- 2.2.10.19 LANCE Reject Physical Address Test LANSREJECT\_PHY Transmits an internal loop packet with a destination address that differs from the LANCE address; checks that the packet is correctly rejected by the LANCE.

- 2.2.10.20 LANCE Accept Physical Address Test LANSACCEPT\_PHY Transmits an internal loop packet with a destination address equal to the LANCE address; verifies that the packet is correctly transmitted and received.

- 2.2.10.21 LANCE Force Collision Test LANSCOLLISION Checks the LANCE collision detection logic. By setting the RTRY bit in the transmit descriptor, the test verifies that a collision can be forced and reported. A packet is sent in internal loopback, promiscuous mode, with the collision bit set; this enables the LANCE to detect collisions. Transmission is attempted 16 times before the LANCE signals a retry error and terminates the attempt.

- 2.2.10.22 Receive CRC Logic Test LANSRCV\_GOOD\_CRC Ensures that the LANCE receives a correct CRC without flagging CRC errors. Packets are transmitted in promiscuous, internal loopback mode. Transmit CRC generation is disabled, and a calculated CRC is appended to the packet. The receiver checks the CRC against the CRC that it calculated as the packet is received.

- 2.2.10.23 Transmit CRC Logic Test LANSXMT\_CRC Ensures that the LANCE generates and appends a CRC on transmission. A packet transmits in promiscuous, internal loopback mode. The transmitter generates the CRC; the receiver does not check the validity of a received CRC. A CRC is manually calculated, and checked against the CRC that the transmitter appended to the packet.

- 2.2.10.24 Receive Bad CRC Test LANSRCV\_BAD\_CRC Ensures that the LANCE detects bad CRCs. Packets are transmitted in promiscuous, internal loopback mode with a bad CRC appended to the packet. The receiver flags CRC errors.

- 2.2.10.25 LANCE Broadcast Address and Byte Swap Test LANSBROADCAST Ensures that the LANCE accepts an internal loopback packet with a destination address equal to the broadcast address. This test is run in Byte Swap Mode.

- 2.2.10.26 LANCE Multicast Address Test LANSMULTICAST Ensures that the LANCE accepts or rejects frames based on group logical addresses.

- 2.2.10.27 External Loopback Test LANSEXTERNAL\_LOOP Ensures that the LANCE can correctly transmit and receive external loopback packets. This also tests the Serial Interface Adapter (SIA).

- 2.2.10.28 Length, Parity, Initialize Sequence RTSCHAR\_LENGTH Tests each channel for the correct interrupting sequence, character length, and parity generation. The receivers are initialized to interrupt on RXRDY. The receiver identifies the different character lengths and the different parity types of the four characters that are transmitted.

- 2.2.10.29 **DUART Transmit/Receive Break Test RT\$BREAK —** Tests the ability of each of the Receive/Transmit channels to detect and accurately report a break character.

- 2.2.10.30 Force Framing Error Test RTSFRAMING Tests the ability of each channel to detect various framing errors and executes only in external loopback mode.

- 2.2.10.31 Force Overrun Error, FIFO Depth Check Test RTSOVERRUN Tests that each DUART channel accurately reports a receive overrun error.

- 2.2.10.32 Baud Rates Test RTSBAUD\_RATE Tests that each channel transmits and receives at several different baud rates.

- 2.2.10.33 System Exerciser Test ST\$EXERCISER Exercises much of the router system hardware. Data transmits and is received on each terminal port and the network interconnect (NI) port while modem control interrupts are posted. The following devices are active while this test executes:

- General Purpose (GP) Timer Interrupts every 10 milliseconds.

- Refresh Timer Interrupts every 3.8 milliseconds.

- **EEPROM** Accessed to read data from EEPROM. The write inhibit circuitry is exercised without performing a write.

- PAM and Parity Detection/Generation The DUART and LANCE buffers are in RAM, and the RAM and parity detection/generation logic is used during testing.

- NI PROM, PROM, and I/O Blocks Accessed during testing.

- Watchdog Timer Active during testing.

- LANCE Accessed while in operation.

Self-Test 2-9

### 2.2.11 Self-Test Error Codes

Error information is stored in Initialized-RAM, with the error information start address at \$8014A. A Failing Test byte indicates the test in which an error is detected. For example, if ST\$QUICKRAM fails, test number 3 is written to the Failing Test byte, as shown in Table 2-2. The error number identifies the part of the test in which an error is detected. A test can generate decimal error codes from 1 to 99.

The ERROR DATA section contains test specific data, for example, when RAM TEST detects an error while writing to location \$1040. Error data contains the address of the failures, and the bits in error.

Description

Table 2-4 categorizes and defines the various Self-test error codes.

Table 2-4: Self-Test Error Codes

rt\$k\_cum\_failure

rtSk\_icn1\_err

Message

Page/Fall Error Codes

Code

| 00      | st\$k_success      | Operation successful                       |

|---------|--------------------|--------------------------------------------|

| 01      | st\$kfailure       | Operation failed                           |

| General | Error Codes        |                                            |

| 1       | e <del>rr</del> I  | First error check failed                   |

| 2       | err 2              | Second error check failed                  |

| 3       | err 3              | Third error check failed                   |

| 4       | err 4              | Fourth error check failed                  |

| 5       | err 5              | Fifth error check failed                   |

| 6       | err 6              | Sixth error check failed                   |

| 7       | err -              | Seventh error check failed                 |

| 8       | err 8              | Eighth error check failed                  |

| 9       | err 9              | Ninth error check failed                   |

| DUART   | Error Codes        |                                            |

| 11      | rt\$k_xmt_timeout  | A transmit interrupt did not occur on time |

| 12      | rt\$k_rct_timeout  | A receive interrupt did not occur on time  |

| 13      | rt\$k_rcv_cbar_err | A bad character was received               |

| 14      | rt&k_rci_stat_err  | A bad status was received                  |

|         |                    |                                            |

All ports failed

Number of interrupts incorrect

(continued on next page)

15

16

| Codo                     | Meccege                | Description                                            |  |  |

|--------------------------|------------------------|--------------------------------------------------------|--|--|

| LANCE                    | Error Codes            |                                                        |  |  |

| 21                       | lan\$k_no_read_init    | The initialize block was not read                      |  |  |

| 22                       | lan3k_rcv_desc_err     | The error bit is set in the receive descriptor         |  |  |

| 23                       | lanskrcvdesctimeout    | A timeout occurred for possession of the descriptor    |  |  |

| 24                       | lan\$krcvtimeout       | A receive interrupt did not occur                      |  |  |

| 25                       | lan\$diffbuffsize      | The transmit and receive buffers are different in size |  |  |

| 26                       | lan3_diff_buffers      | The transmit and receive buffers are different         |  |  |

| 27                       | lans_bad_rcv_buff_crc  | An incorrect CRC is stored in the receive buffer       |  |  |

| 28                       | lan\$_xmt_desc_err     | The error bit is set in the transmit descriptor        |  |  |

| 29                       | lan\$_xml_desc_timeout | A timeout occurred for possession of the descriptor    |  |  |

| 2A                       | lans_xmt_timeout       | A transmit interrupt did not occur on time             |  |  |

| 2B                       | lan3_csr0_err          | An error bit is set in CSR0                            |  |  |

| <b>2C</b>                | lan3_no_stop           | LANCE did not stop                                     |  |  |

| 2D                       | lans_no_exp_err        | LANCE did not flag an expected error                   |  |  |

| Asynchronous Error Codes |                        |                                                        |  |  |

| 70                       | st8k_ui_err            | Unexpected interrupt error                             |  |  |

| 71                       | st\$k_par_err          | Parity error                                           |  |  |

| 72                       | st8k_unx_rt_int        | Unexpected DUART interrupt                             |  |  |

| 73                       | st8k_warm_err          | Illegal warmstart reset                                |  |  |

| 74                       | st8k_warm_err          | Illegal warmstart and a bad stack                      |  |  |

### NOTE

Typical asynchronous errors are unexpected interrupts and parity errors. Error codes are written to EEPROM under Error Number. Following is an example of an EEPROM error display when Self-test fails:

Failing Test: 03 € 8014B Error Number: 71 € 8014D Error Data: 00 € 8014F

This indicates that Test 3 (ST\$QUICK\_RAM) failed due to a parity error, 71(hex).

# 3 Initialize Program

#### 3.1 Introduction

The initialize program is in the Program ROM and starts on completion of the Self-test program or on detection of a fatal bugcheck error.

After Self-test, the initialize program transmits a request for a down-line load of the router image from a load host. When Self-test detects a fatal hardware error or the Ethernet loopback test failed, no request is sent. An active DECnet Phase IV host is needed to operate the router.

The initialize program is started by the router manager and the program issues a request for an upline dump of Program RAM on a fatal bugcheck. The watchdog timer also initializes up-line dump requests.

The initialize program supports the following router start-up and operating functions:

- Part 1 transmits a request program load message on the Ethernet for a down-line load of the router software image.

- Part 2 processes down-line load records from the load host, stores the router software in program RAM, and displays the load status on the terminal.

- Part 3 displays a fatal bugcheck message on the terminal when a fatal error condition is detected by the operating software.

- Part 4 when enabled, transmits an up-line dump of all router program RAM locations to a dump host after a fatal bugcheck.

#### 3.2 Down-Line Load

The initialize program displays meusages on the terminal to show the progress of a down-line load procedure.

# 3.2.1 Down-Line Load Messages

When Self-test does not detect errors, LED 3 lights and stays on. When a software error occurs, LED 3 blinks signaling that operating software has not been loaded. When the load starts, the router Ethernet address and firmware version number is displayed. A second message gives the status of the image load. The second message repeats every 30 seconds when the load fails, or when a load host volunteer is not available.

The following sequence of messages appears on the terminal screen at 30-second intervals:

```